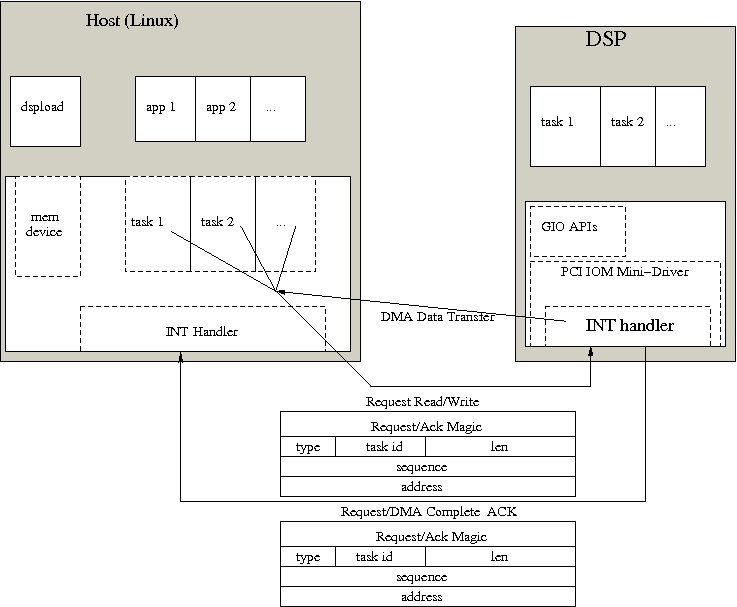

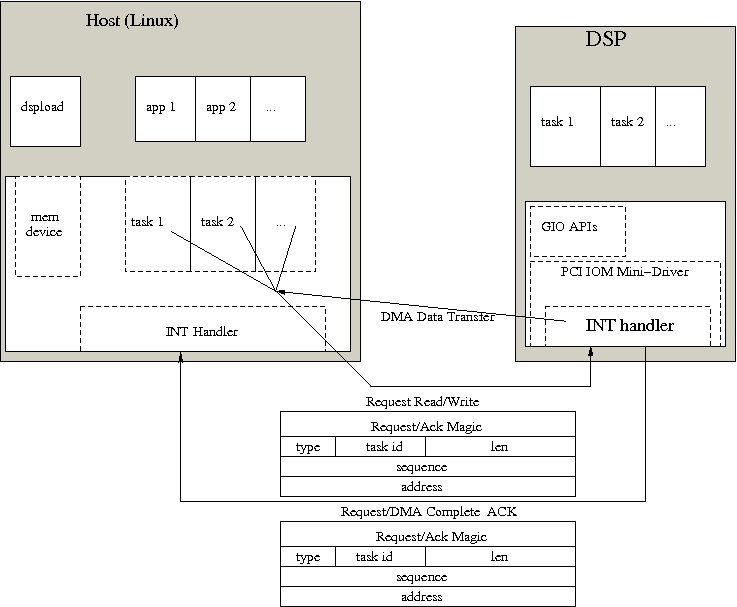

The DM642 pci driver is a simple but effective general purpose, policy-free driver for developers.This development package provides a complete Host-side driver(linux 2.6), a Dsp-side DSP/BIOS PCI IOM mini-driver and some examples for the TMS320DM642 chipset family from Texas Instruments.

+---linux

| +---driver

| \---apps

| +---dspload

| \---samples

| +----mmap_loop.c

| +----rw_loop.c

|

...

\---target

+---iom_driver

+---sync_pci

cvs -d:pserver:anonymous@dm642-pci.cvs.sourceforge.net:/cvsroot/dm642-pci login

cvs -z3 -d:pserver:anonymous@dm642-pci.cvs.sourceforge.net:/cvsroot/dm642-pci co -P dm642_pci

the driver is successfully build under Linux version 2.6.15-1.2054_FC5.

cd linux/driver

make

./dm642_load (load the dm642_pci.ko module and create correspondence devices, adapt from LDD3 examples)

cd linux/apps/dspload

make

./dspload ../../../target/sync_pci/sync_pci.out (load the dsp side app)

cd linux/samples

make

./rw_loop 30000 1

read/write test: bufsize=30000, loopcnt=1, dev_name=/dev/dm642_pci1

io time(us): avg = 5739, min = 5739, max = 5739, last = 5739dmesg (use dmesg see DSP-side app print output and driver's printk. another method: killall klogd; cat /proc/kmsg)

<7>dm642_interrupt: write spend time(us): 005304 CPU cycles: 12706366

<7>dm642_interrupt: read spend time(us): 005486 CPU cycles: 13142106

<4>DSP loop_tsk(1/4): can accept max TRANSFER_COUNT is 32760

<4>DSP loop_tsk(0/4): can accept max TRANSFER_COUNT is 32760

<4>DSP read_tsk(3/4): can accept max TRANSFER_COUNT is 32760

<4>DSP write_tsk(2/4): can accept max TRANSFER_COUNT is 32760

<4>DSP DMA READ(0e810000 -> 00000768 30000) time(DSP cycles): 3172568

<4>DSP DMA WRITE(00000768 -> 0e568000 30000) time(DSP cycles): 138400

./dspload ../../../target/sync_pci/sync_pci.out

./mmap_loop 30000 1

mmap test: bufsize=30000, loopcnt=1, dev_name=/dev/dm642_pci1

0: 00018000 -> b7f6b000

1: 00020000 -> b7f5b000

2: 00028000 -> b7f53000

bufs for write: 3

0: 00000000 -> b7f4b000

1: 00008000 -> b7f43000

2: 00010000 -> b7f3b000

bufs for read: 3

io time(us): avg = 5618, min = 5618, max = 5618, last = 5618dmesg

<7>dm642_interrupt: write spend time(us): 005287 CPU cycles: 12662902

<7>dm642_interrupt: read spend time(us): 005618 CPU cycles: 13456524

<4>DSP loop_tsk(1/4): can accept max TRANSFER_COUNT is 32760

<4>DSP loop_tsk(0/4): can accept max TRANSFER_COUNT is 32760

<4>DSP read_tsk(3/4): can accept max TRANSFER_COUNT is 32760

<4>DSP write_tsk(2/4): can accept max TRANSFER_COUNT is 32760

<4>DSP DMA READ(0e810000 -> 00000768 30000) time(DSP cycles): 3162064

<4>DSP DMA WRITE(00000768 -> 0f210000 30000) time(DSP cycles): 138360

./dspload ../../../target/sync_pci/sync_pci.out

./read_3 30000 3

read/write test: bufsize=30000, loopcnt=3, dev_name=/dev/dm642_pci3

0 hello,world!

1 hello,world!

2 hello,world!

io time(us): avg = 347, min = 318, max = 397, last = 318cat /proc/kmsg (run on another terminal, before run ./read_3 30000 3)

<7>dm642_interrupt: read spend time(us): 000246 CPU cycles: 591636

<4>DSP loop_tsk(1/4): can accept max TRANSFER_COUNT is 32760

<4>DSP loop_tsk(0/4): can accept max TRANSFER_COUNT is 32760

<4>DSP read_tsk(3/4): can accept max TRANSFER_COUNT is 32760

<4>DSP write_tsk(2/4): can accept max TRANSFER_COUNT is 32760

<4>DSP DMA WRITE(00000768 -> 0e430000 30000) time(DSP cycles): 138944

<7>dm642_interrupt: read spend time(us): 000246 CPU cycles: 590448

<4>DSP DMA WRITE(00000768 -> 09f18000 30000) time(DSP cycles): 138824

<7>dm642_interrupt: read spend time(us): 000243 CPU cycles: 585482

<4>DSP DMA WRITE(00000768 -> 0a658000 30000) time(DSP cycles): 137888

"dma time"(DMA complete - DMA start) is counted on DSP side use TIMER COUNT REGISTER(unit CPU cycles/8) DM642 is runing at 600MHz. the examples list above have multiplied by 8.

"request time"(from the request time to received request complete ack) is counted on Host side use get_cycles/rdtscl, CPU is running at 2.4GHz.

"user time"(before read call to read call end) is counted on Host side use gettimeofday.

Copyright ©2005-2007 by W&Y

This page is generated by Google Docs & Spreadsheets.